【设计经验】PCB设计规范(下)

经过上期文章的介绍,想必大家都已经对PCB设计中布局的部分有了充分的了解。(错过上期文章的朋友请戳这里)那么本篇文章将为您详细解析“排线的秘诀”

PCB的排线工作,千变万化终究不过是为了一个简单的目标——尽量减少不必要的干扰。为了这个目标,机智的工程师们几乎什么事都能做的出来,让我们来逐条分析:

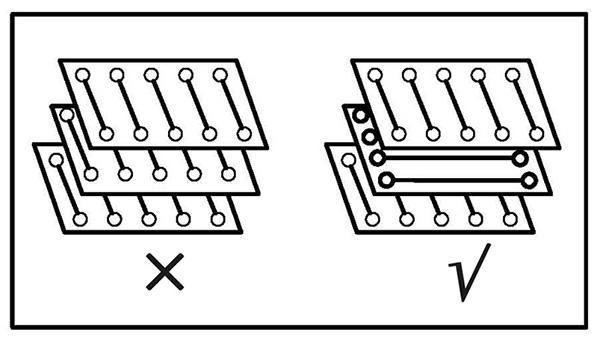

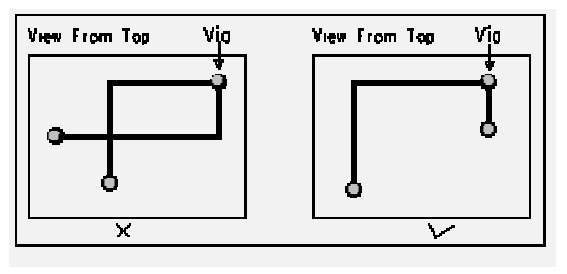

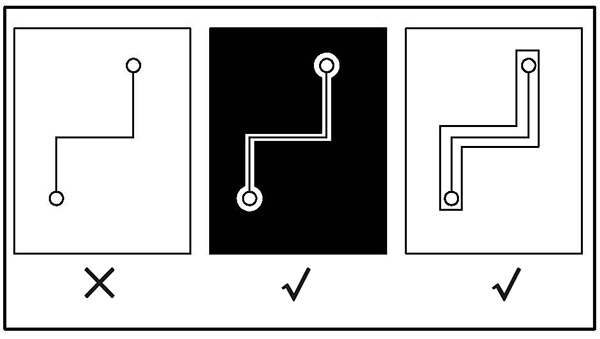

当我们开始布线,就应该步步为营了。看似平淡的方向、长度或者是倒角,都是杀机重重。方向来说,相邻层的走线方向要成正交结构(如下图),若不这样做烦人的层间窜扰必将成为你的心腹大患。但如果你的板结构限制了你不能这么做,那么你可以考虑用地平面隔离各布线层,用地信号线隔离各信号线。

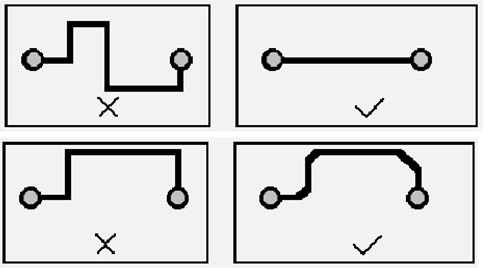

而在长度上来说,尽量短的布线可以有效减少干扰发生的概率,对于一些重要信号线,如时钟线,将其振荡器放在离器件很近的地方无疑是个明智的决定。而对驱动多个器件的情况,应根据具体情况决定采用何种网络拓扑结构。而在倒角方面应避免产生锐角和直角, 产生不必要的辐射的同时也会降低工艺性能。

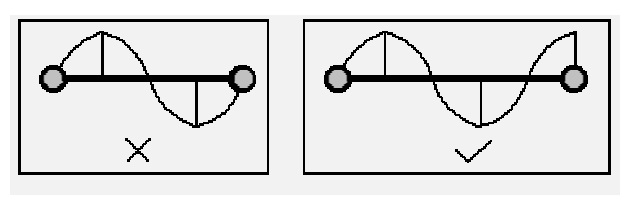

针对高频信号设计而言, 布线长度应保证不得与其波长成整数倍关系, 以免产生谐振现象。

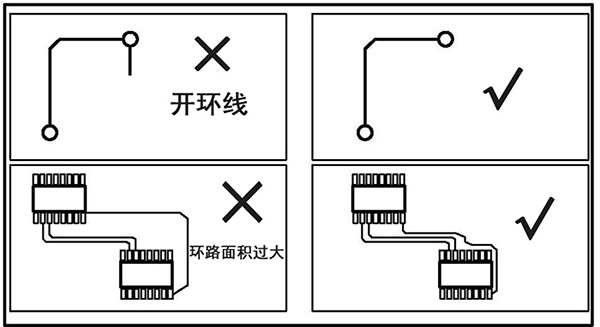

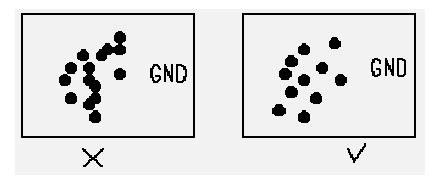

作为一个电信号左冲右突的场景,稍有不慎就可能导致天线效应,带来丰富的干扰。这种情况无疑是需要被避免的,那么哪些情况会导致天线效应呢?浮空的布线、环面积大的回路、孤立的铜区(死铜)

有些新手工程师可能会想当然的在空白区域铺上一大片孤立的铜区来增强PCB的强度和辅助散热,但这样做的隐患还是很大的。并不建议这样来做。而在设计多层板时,信号线在不同层间也可能形成自环成为天线。设计时应尽力避免。

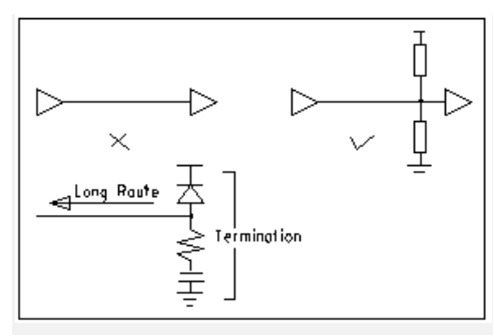

山花对海树,赤日对苍穹,凡事都应当讲究个匹配才能相得益彰。PCB的设计同样是如此,在设计PCB时要尽量选择匹配相同的线宽来保证阻抗的连续,在某些复杂的情况下增加终端电阻来保证阻抗匹配也是常见的做法。

为了保证信号的输入和输出阻抗与传输线的阻抗正确匹配,可以采用多种形式的匹配方法, 所选择的匹配方法与网络的连接方式和布线的拓朴结构有关。

A. 对于点对点(一个输出对应一个输入) 连接, 可以选择始端串联匹配或终端并联匹配。

B. 对于点对多点(一个输出对应多个输出) 连接, 当网络的拓朴结构为菊花链时,应选择终端并联匹配。当网络为星型结构时,可以参考点对点结构。星形和菊花链为两种基本的拓扑结构, 其他结构可看成基本结构的变形, 可采取一些灵活措施进行匹配。

在实际操作中要兼顾成本、 功耗和性能等因素, 一般不追求完全匹配,只要将失配引起的反射等干扰限制在可接受的范围即可。

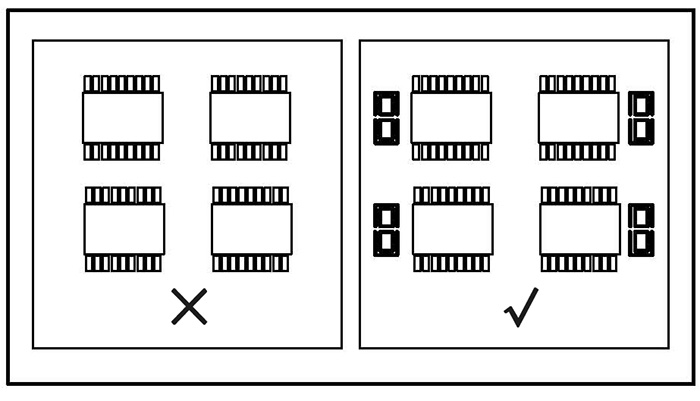

为了满足驱动电路电流的变化,避免耦合干扰,去耦电阻的匹配也是十分重要的,尤其是使用双层板,去藕电容的布局及电源的布线方式将直接影响到整个系统的稳定性。

为了防止不同工作频率的模块之间的互相干扰,在缩短高频部分布线长度的同时,器件也应当保持分层/分区走线。对于导通孔密集的区域,要注意避免孔在电源和地层的挖空区域相互连接,形成对平面层的分割,从而破坏 平面层的完整性,并进而导致信号线在地层的回路面积增大。

对一些特别重要,频率特别高的信号,如时钟信号,同步信号;应该考虑领导干部特殊化,采用铜轴电缆屏蔽结构设计,即将所布的线上下左右用地线隔离而且还要考虑好如何有效的让屏蔽地与实际地平面有效结合。

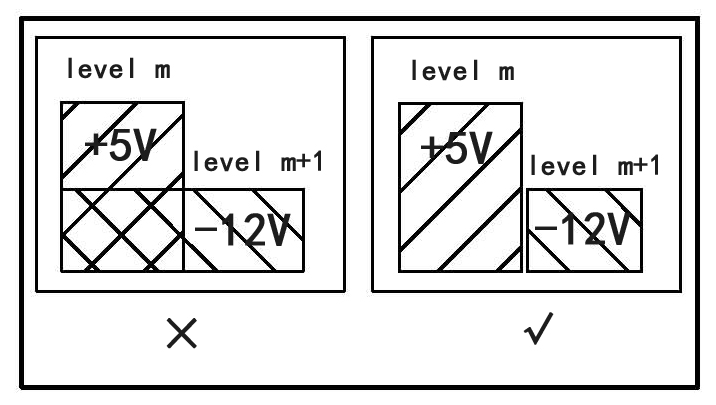

而不同电源层在空间上要避免重叠。 这样可以减少不同电源之间的干扰, 特别是一些电压相差很大的电源之间, 电源平面的重叠问题一定要设法避免, 难以避免时可考虑中间隔地层。

前面的种种,均是定性的来说明PCB走线时应该注意的要点。定量的来看走线问题那么主要有以下几点:

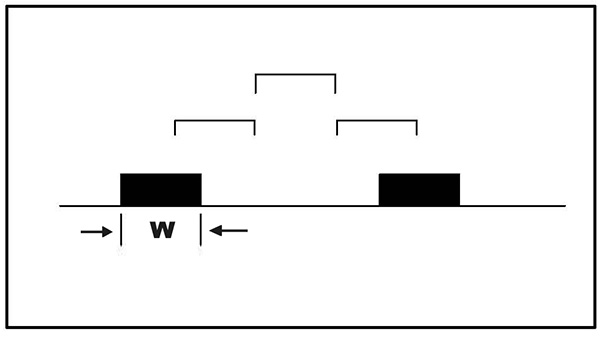

A.3W原则

为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。

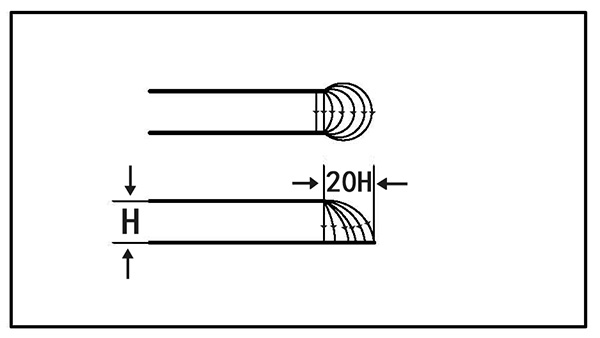

B.20H原则

为防止板边幅射,在设计时应将电源层内缩。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内

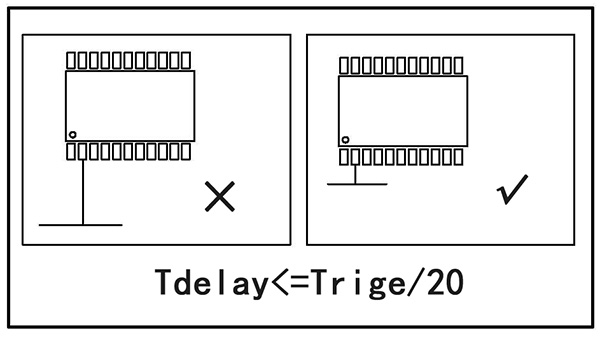

C.走线的分枝长度控制规则

尽量控制分枝的长度,一般的要求是Tdelay<=Trise/20。

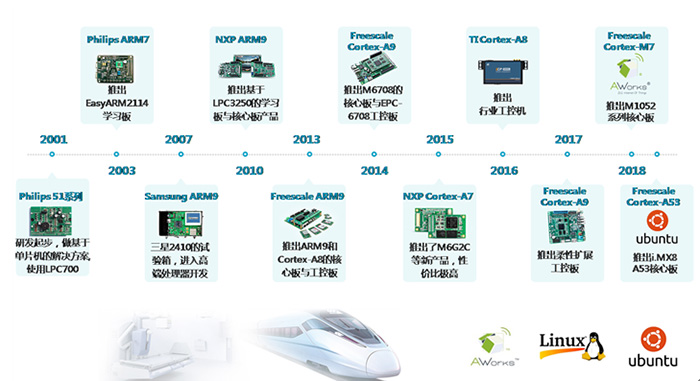

嵌入式技术是米乐官方版m6(中国)官方网站IOS/安卓通用版/手机APP成长与发展的核心竞争力,我们自2001年从8位单片机方案设计开始,逐步掌握Arm7™、Arm9™、Cortex ®-A7、A8、A9、M7等Arm®体系的处理器应用技术,拥有全系列的工业级Arm®核心板与工控机。同时,基于对嵌入式技术的理解与积累,我们自主研发下一代软件开发平台-AWorksLP工业智能物联开发平台,帮助用户基于稳定的软硬件平台快速实现米乐官方版m6(中国)官方网站IOS/安卓通用版/手机APP开发。